Hello ZigZagJoe: I am really impressed and I know I am the guy you will enjoy working with hopefully sir. KUDO's!

I've been carrying the NeXT torch as an incredible career rescuing heck I've jumped in front of a bulldozer in a landfill at the School of mines (true story) to save some.

repairing, trading , reselling, maintaining buying and selling NeXT hardware, software and memorabilia for the past 32 years lol amazing like the MayTag repairmen . I and the NeXT Community have wanted this upgrade to manifest for so long, this is epic, thank you

I suffer from an ailment called aging and with my health conditions working from home using a walker works out well.

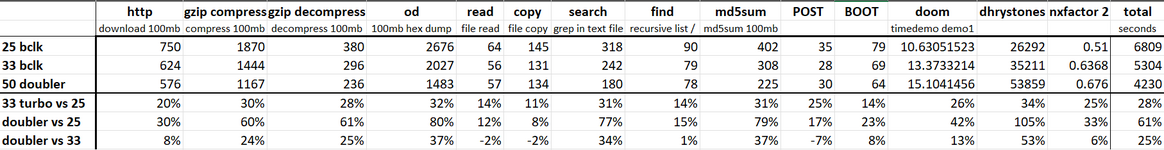

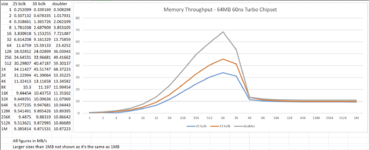

The Turbo Color 50 Mhz hack, I am the current owner by the way but it was a galliant effort in 2003 and I also own a NeXT 40 Mhz Nitro and a few hundred NeXT workstations and Cubes. I will happily donate some NeXT motherboards if you need them to your cause . Obviously 68040 25Mhz and 68030 25Mhz Cube Boards . I also have Larry Ellisons Turbo Color and NeXT Cubes number 4 and 5

My youtube.com//robblessin channel shows hundreds of my NeXT and other projects some of them ecletic sense of humor.

Yes, Apologies about the confusing registering for the nextcomputers.org forum , it isn't a right of passage , it is because we were being attacked by bots that ran a denial of service attack? What ever it was removing the registration form page for sanity, over whelming the registration process , 80,000 fake registrations in 1 day then once the damn thing beat the registration form , it got worse by start machine gun blasting the threads with spam , putting Nitro our sys admin into a hellscape nightmare of unwinding a spaghetti monster , back up solved it . It seems like we may be able to set up an enquiry button just thought of it, if you all have any ideas or expertise we welcome them.

It was equivalent to 10,000 drones flying into your house all at once and crapping all over the place, the damn thing even booted me at one point , a few weeks of it was enough. Why our site as we are friendly , My name is Rob also computerpowwow on eBay band blackholeinc.com , over hauling the site as well.

Cloud Flair handles it now , we would love to have you , if you would like to join that goes to everyone here you can email me direct at

bhi1@ix.netcom.com , My handle is rob blessin black hole

Your preferred user name and email and I'll make sure nitro gets the info. I'm also battling spam deleting hundreds of messages a day and yes I have a spam filter , I love my job.

I'm also recognizing some members in the threads here , very cool , I had signed up awhile back , so many things in my orbit this is incredible news and

ZIG Zag , we may have done business before .

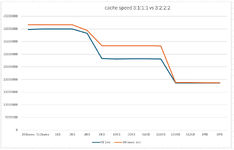

PS I'm also one of the coauthors of Inside NeXT and we are working on the 2025 edition as of a few days ago and Luciano the author , we have few pages to fill and if you like I think is worthy of an addition I appreciate your time and look forward to hearing from you. Best Regards Rob Blessin