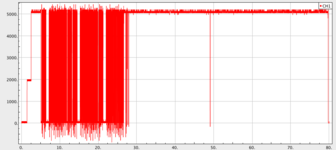

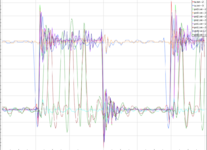

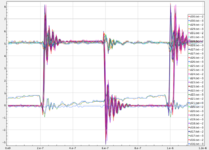

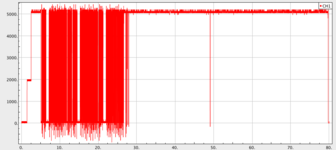

I decided to go back to my old 840AV after ~20years. Similar to other stories I read on this site: powers up, no chime, checkerboard video, no boot. Re-capped, probed supplies: all fine, probed some of the '040 pins. It seems the CPU runs for ~30" (see R/W trace below) then stops. The address on the bus when it stops is $A1E4, consistently across reboots. /BG is asserted low and clock is running fine, so it seems the CPU is waiting for somebody to respond on that address. According to some memory maps I found that address maps to the NU-BUS space, but there is no card plugged in.

Any idea what might be happening?

Thanks, GLM

Any idea what might be happening?

Thanks, GLM