ironborn65

Well-known member

My conquest here

68kmla.org

is being salvaged.. at least I'm trying to.

68kmla.org

is being salvaged.. at least I'm trying to.

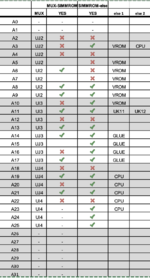

I removed the obvious destroyed chips: RTC, D1, D2 (caps are the easy thing) and the RAM muxes UJ1, UJ2, UJ3.

I'm now looking for continuity, the traces from the muxes to the ROM SIMM.

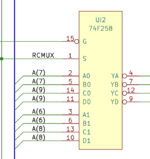

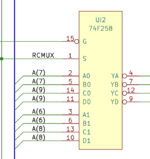

The inputs are in pairs, e.g.: for UI2, A(7) in 2,5, A(9) in 11,14, A(6) in 3,6, A(8) 10, 13. ...

But I was surprised to notice that A(9) and A(8) are shorted, i.e. pins 31 and 32 in the ROM SIMM.

For the other muxes, there are no shorts in the corresponding lines.

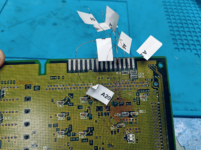

After some thorough checking, I decided that "The mux is shorted" so I desoldered it but "what?", it's still shorted!

In the picture below(*) IMHO red and yellow arrows are supposed to be separated but they are instead shorted.

Does it make sense?

The PCB was cleaned in vinegar, IPA, dishwasher and in the ultrasonic cleaner.

(*) yes, traces and pads are not in good shape, but at least I'll improve my soldering skills and the schematics of the SE/30.

View attachment 79401

Salvaging a bombed SE/30

Hi guys, For a decent price I found a bombed SE/30 that can hopefully be salvaged. A reloaded board is the B plan. As I got it: after a round in the dishwasher and some scrubbing with vinegar: I need to keep scrubbing and rubbing, more washing and rinsing ... At this moment it does...

68kmla.org

68kmla.org

I removed the obvious destroyed chips: RTC, D1, D2 (caps are the easy thing) and the RAM muxes UJ1, UJ2, UJ3.

I'm now looking for continuity, the traces from the muxes to the ROM SIMM.

The inputs are in pairs, e.g.: for UI2, A(7) in 2,5, A(9) in 11,14, A(6) in 3,6, A(8) 10, 13. ...

But I was surprised to notice that A(9) and A(8) are shorted, i.e. pins 31 and 32 in the ROM SIMM.

For the other muxes, there are no shorts in the corresponding lines.

After some thorough checking, I decided that "The mux is shorted" so I desoldered it but "what?", it's still shorted!

In the picture below(*) IMHO red and yellow arrows are supposed to be separated but they are instead shorted.

Does it make sense?

The PCB was cleaned in vinegar, IPA, dishwasher and in the ultrasonic cleaner.

(*) yes, traces and pads are not in good shape, but at least I'll improve my soldering skills and the schematics of the SE/30.

View attachment 79401