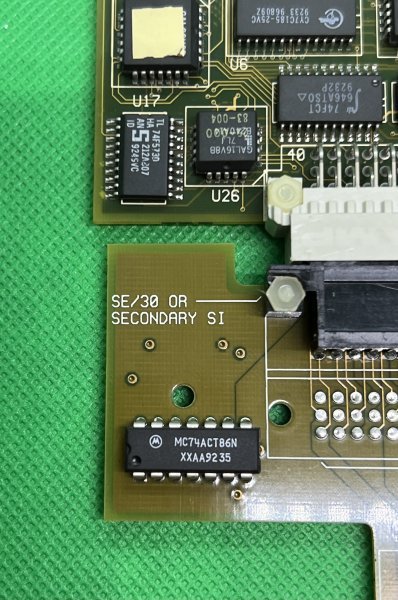

@nottomhanks Thanks, very nice pictures! Very nicely routed design, very efficient use of the two outer layers to be able to route to the FPU with minimum use of via; I can only see 8 vias for A1-A4 (4 below the FPU, 4 underneath it) which are going bottom-top-bottom layers. Everything else seem to be routed on a single layer only. I'm assuming they have two internal layers for power planes, as +5V and GND are not visibly connected to anything (quite noticeably for the capacitors). Not sure shy they felt they needed a couple of capacitors on the opposite side of the FPU - if it was for the FPU, still plenty of space closer to it, above it in the area of C1 and C2.

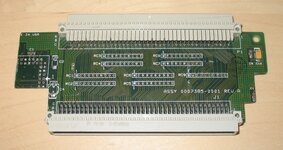

Some interesting details about the routing Looking at the third picture (2446), the connections between the two PDS slots, closest to the FPU. The three thicker lines are power connections for +12V/-5V/-12V. Just above them, connecting the third rows (or rotated columns) of three pins, the routing is different from all the others signals despite the connection pattern being the same. The signal are longer and less close to one another (the 2nd and 4th rows as GND and +5V so connected to internal layers, leaving some available space). Those three are clocks (cpuclk, viaclk, and c16m). Not sure why they felt they needed the breathing room at the expense of length. Strangely, I can only see two connections from that area in the first picture between the motherboard-side connector and the middle PDS!

And it seems /RBV (A1 on the mobo connector) is also connected between the two PDS despite being a 'reserved' pin in those - most other 'reserved' signals aren't. And it doesn't seem to be connected to the mobo connector either, only two traces near those pins which are probably /NUBUS and /PWR (both specified in both the PDS and mobo connector).

Not sure how useful those are in the modern era (finding two useful and compatible PDS cards is going to be difficult...), but with such detailed views of the routing they should be reasonably easy to replicate. Approximate measurement on the pictures says the two PDS connectors are roughly 24.13mm / 0.95in from one another? All parts are still available from Mouser, including the PLCC socket. Might be harder to recreate the routing to use a PGA socket instead as it's quite tight in there.

Some interesting details about the routing Looking at the third picture (2446), the connections between the two PDS slots, closest to the FPU. The three thicker lines are power connections for +12V/-5V/-12V. Just above them, connecting the third rows (or rotated columns) of three pins, the routing is different from all the others signals despite the connection pattern being the same. The signal are longer and less close to one another (the 2nd and 4th rows as GND and +5V so connected to internal layers, leaving some available space). Those three are clocks (cpuclk, viaclk, and c16m). Not sure why they felt they needed the breathing room at the expense of length. Strangely, I can only see two connections from that area in the first picture between the motherboard-side connector and the middle PDS!

And it seems /RBV (A1 on the mobo connector) is also connected between the two PDS despite being a 'reserved' pin in those - most other 'reserved' signals aren't. And it doesn't seem to be connected to the mobo connector either, only two traces near those pins which are probably /NUBUS and /PWR (both specified in both the PDS and mobo connector).

Not sure how useful those are in the modern era (finding two useful and compatible PDS cards is going to be difficult...), but with such detailed views of the routing they should be reasonably easy to replicate. Approximate measurement on the pictures says the two PDS connectors are roughly 24.13mm / 0.95in from one another? All parts are still available from Mouser, including the PLCC socket. Might be harder to recreate the routing to use a PGA socket instead as it's quite tight in there.