-

Updated 2023-07-12: Hello, Guest! Welcome back, and be sure to check out this follow-up post about our outage a week or so ago.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

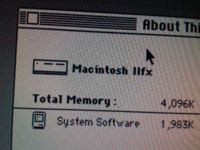

My IIfx progress

- Thread starter SophieRose

- Start date

Phipli

Well-known member

Try wiring a through hole ceramic capacitor over the power pins on chips in the area. Perhaps you're modifying the capacitance on chips with the IPA. Perhaps there are broken traces to decoupling capacitors.Ive narowed it down to UD16.. it boots and works fine if i put iso on and around UD16.. weird. Otherwise it just does bad chime and no video. Its not the cooling effect cos I tried freezer spray and no joy. UD16 is the SRAM connected to the serial asic.

View attachment 56558

View attachment 56559

View attachment 56560

0.1uF is probably a reasonable value.

ObeyDaleks

Well-known member

Ignore my post, I looked it up and apparently pure IPA is non-conductive. Learned something new today.

Last edited:

ClassicGuyPhilly

Well-known member

SophieRose

Well-known member

A couple around the serial asic.. looked fine but the via was not doing its job due to battery spill rot.Good progress. Out of curiosity which traces did you have to repair?

Thanks.. That's what I love about this forum.. ☺some great folks on here.Watching your progress and cheering you on! Also no surprise Mr. IIfx @joshc is here helping out as he has with my new IIfx journey.

SophieRose

Well-known member

mdeverhart

Well-known member

When the machine is off, what’s the resistance between /WE (pin 27) and 5V, and between /WE and GND?

If /WE is stuck low the contents of the SRAM will likely get scrambled, as it’ll latch new data when it shouldn’t. The Serial ASIC should only drive /WE low when it wants to write data.

If /WE is always low, there are 3 possibilities:

1. /WE is partially shorted to GND, so the Serial ASIC can’t drive it high. Fixing this would mean finding and fixing the short. Could be cap goo under the Serial ASIC or SRAM, or in that area.

2. /WE is a push-pull output from the Serial ASIC, and it can’t drive it high anymore due to damage to the Serial ASIC.

3. /WE is an open drain output from the Serial ASIC, and the pull-up resistor (either inside the ASIC or on the board) is broken and can’t pull /WE up anymore. The Bomarc schematic doesn’t show a pull-up on the board, but it’s possible it’s just not shown.

Fixing #2 or #3 might require replacing the Serial ASIC (probably very hard to source). Fixing #3 if there’s a bad pull-up resistor should be as easy as finding it and replacing it.

The other option (bit of a bodge) would be to replicate what you’ve done with the IPA - add your own pull-up resistor between /WE and 5V. You could solder a resistor between pins 27 and 28, which would probably work. That said, I’d want to see the resistance measurements I mentioned above before recommending this.

If /WE is stuck low the contents of the SRAM will likely get scrambled, as it’ll latch new data when it shouldn’t. The Serial ASIC should only drive /WE low when it wants to write data.

If /WE is always low, there are 3 possibilities:

1. /WE is partially shorted to GND, so the Serial ASIC can’t drive it high. Fixing this would mean finding and fixing the short. Could be cap goo under the Serial ASIC or SRAM, or in that area.

2. /WE is a push-pull output from the Serial ASIC, and it can’t drive it high anymore due to damage to the Serial ASIC.

3. /WE is an open drain output from the Serial ASIC, and the pull-up resistor (either inside the ASIC or on the board) is broken and can’t pull /WE up anymore. The Bomarc schematic doesn’t show a pull-up on the board, but it’s possible it’s just not shown.

Fixing #2 or #3 might require replacing the Serial ASIC (probably very hard to source). Fixing #3 if there’s a bad pull-up resistor should be as easy as finding it and replacing it.

The other option (bit of a bodge) would be to replicate what you’ve done with the IPA - add your own pull-up resistor between /WE and 5V. You could solder a resistor between pins 27 and 28, which would probably work. That said, I’d want to see the resistance measurements I mentioned above before recommending this.

ClassicGuyPhilly

Well-known member

So I only understood maybe half of the above, but you blew my mind @mdeverhart !

mdeverhart

Well-known member

Hah! I’d be happy to explain in more depth, but we should probably start another thread for that discussion. Great troubleshooting @SophieRose!So I only understood maybe half of the above, but you blew my mind @mdeverhart !

SophieRose

Well-known member

Okeydokey cheers @mdeverhartHah! I’d be happy to explain in more depth, but we should probably start another thread for that discussion. Great troubleshooting @SophieRose!

I took these readings..

Betweeen pin 27 and 28(5v) 469ohms

Between pin 27 and gnd.. 452ohms

Between pin 28(5v) and gnd.. 15 ohms

I was thinking along the same lines but wouldnt know what value resistor to add. Ive checked around there and theres no pull up resistors on the board.

Also check continuity between pins 27 of the SRAM and 71 of the ASIC if you haven't already. If that trace is broken, pin 27 is floating and can cause trouble by registering low.I took these readings..

SophieRose

Well-known member

Yeah did that.. it's a straight connection.. only other thing I can think of doing is lifting pin 71 of the asic and seeing what the resistance is then between the pin and gnd and the now unoccupied trace n gnd just to confirm.. but i recon the asic is at fault here.Also check continuity between pins 27 of the SRAM and 71 of the ASIC if you haven't already. If that trace is broken, pin 27 is floating and can cause trouble by registering low.

ClassicGuyPhilly

Well-known member

Thanks but I'm good for now, just enjoying watching from the sidelines as you all put on quite a technical show.(I'll Google how latching works, sounds interesting). I never studied computing at these levels, appreciating the opportunity to expand my knowledge. Keep going team!Hah! I’d be happy to explain in more depth, but we should probably start another thread for that discussion.

mdeverhart

Well-known member

Hmm… resistance measurements don’t look too bad. I’m not sure what normal would be, but for a partial short I’d expect something < 100 Ohms. For comparison, can you measure the resistance between /OE (pin 22) and 5V and between /OE and GND?

Lifting pin 71 on the ASIC to isolate might be a good intermediate step, but given the resistance measurements I’m not sure it’s necessary yet.

Was there any capacitor leakage in the area? Is the /WE trace routed straight from the ASIC to the SRAM on the top layer, or does it go through any vias?

Lifting pin 71 on the ASIC to isolate might be a good intermediate step, but given the resistance measurements I’m not sure it’s necessary yet.

Was there any capacitor leakage in the area? Is the /WE trace routed straight from the ASIC to the SRAM on the top layer, or does it go through any vias?

SophieRose

Well-known member

Will check ☺

Last edited:

SophieRose

Well-known member

@mdeverhartHmm… resistance measurements don’t look too bad. I’m not sure what normal would be, but for a partial short I’d expect something < 100 Ohms. For comparison, can you measure the resistance between /OE (pin 22) and 5V and between /OE and GND?

Lifting pin 71 on the ASIC to isolate might be a good intermediate step, but given the resistance measurements I’m not sure it’s necessary yet.

Was there any capacitor leakage in the area? Is the /WE trace routed straight from the ASIC to the SRAM on the top layer, or does it go through any vias?

Between pin 22 and 28(5v) its 508 ohms

And pin 22 and gnd is 521 ohms.

Pin 27 goes from under the sram ic through a via and then a track on the other side to another via and up under the asic.

Ive checked the other asic/sram combo as its the same setup.

and pin 27 to gnd is 456 ohms.

And pin 27 to pin 285v is 514 ohms.

Thanks for your help btw.. much appreciated.

Last edited:

mdeverhart

Well-known member

Happy to help

All of those resistance measurements look pretty good - nothing obviously wrong at least.

Can you take a resistance measurement between pin 71 on the ASIC and pin 27 on the SRAM? You mentioned that you checked the /WE trace before, but it’s worth checking again.

Also, with the computer on, can you measure the voltage on ASIC pin 71 and at SRAM pin 27?

Some more invasive things you could try:

1. Reflow/touch up the solder on ASIC pin 71 and SRAM pin 27, maybe with just a touch of fresh solder.

2. Solder a bodge wire directly between ASIC pin 71 and SRAM pin 27, bypassing the trace on the board.

3. Solder a 1k pull-up resistor between SRAM pins 27 and 28.

It’s possible #1 or #2 might fix the issue. #3 isn’t likely to actually solve the problem (I wouldn’t be surprised if you had serial port problems if you actually tried to use it), but it might let you bypass the issue for now and get the machine booting consistently.

I’m not too familiar with the IIfx, so I don’t know how the Serial ASIC is used by Mac OS in practice. From a quick look, it looks like you might be able to use the “IIfx Serial Switch” control panel to put the serial into Bypass/Compatibility mode, which might bypass the Serial ASIC. That’s probably something to investigate later after you get the machine booting consistently.

All of those resistance measurements look pretty good - nothing obviously wrong at least.

Can you take a resistance measurement between pin 71 on the ASIC and pin 27 on the SRAM? You mentioned that you checked the /WE trace before, but it’s worth checking again.

Also, with the computer on, can you measure the voltage on ASIC pin 71 and at SRAM pin 27?

Some more invasive things you could try:

1. Reflow/touch up the solder on ASIC pin 71 and SRAM pin 27, maybe with just a touch of fresh solder.

2. Solder a bodge wire directly between ASIC pin 71 and SRAM pin 27, bypassing the trace on the board.

3. Solder a 1k pull-up resistor between SRAM pins 27 and 28.

It’s possible #1 or #2 might fix the issue. #3 isn’t likely to actually solve the problem (I wouldn’t be surprised if you had serial port problems if you actually tried to use it), but it might let you bypass the issue for now and get the machine booting consistently.

I’m not too familiar with the IIfx, so I don’t know how the Serial ASIC is used by Mac OS in practice. From a quick look, it looks like you might be able to use the “IIfx Serial Switch” control panel to put the serial into Bypass/Compatibility mode, which might bypass the Serial ASIC. That’s probably something to investigate later after you get the machine booting consistently.

SophieRose

Well-known member

Similar threads

- Replies

- 6

- Views

- 856

- Replies

- 2

- Views

- 559

- Replies

- 1

- Views

- 463