Hello all, I recently purchased a G4 Cube and scored a 1Ghz Powerlogix CPU upgrade card along with it. I've installed it and it's been running with no issues inside my Cube. I am aware that there is L3 cache on this card as I have check on everymac.com, but I haven't found a way to enable it.

What I have tried:

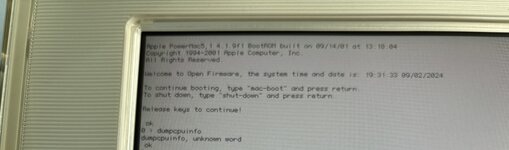

- I've tried downloading all versions of CPU Director, but I keep getting a specific error about not being able to load the current KEXT version for it. (This happened for all versions of CPU Director I've tried). My calendar and clock are all correct.

View attachment IMG_4955.JPG

- I've tried downloading the CD cdr file from macintosh repository, but there seems to be no drivers contained in the cdr that allow me to install to enable the L3 Cache. (Could I have missed it? I don't think so..)

If anyone could help find a way to enable the L3 cache on my board, I'd appreciate it very much!

What I have tried:

- I've tried downloading all versions of CPU Director, but I keep getting a specific error about not being able to load the current KEXT version for it. (This happened for all versions of CPU Director I've tried). My calendar and clock are all correct.

View attachment IMG_4955.JPG

- I've tried downloading the CD cdr file from macintosh repository, but there seems to be no drivers contained in the cdr that allow me to install to enable the L3 Cache. (Could I have missed it? I don't think so..)

If anyone could help find a way to enable the L3 cache on my board, I'd appreciate it very much!