cd "/Volumes/Work/Open Firmware and Name Registry/ROM PowerPC Mac"

xxd "ROM Beige G3 rev D/ROMs/@FFC00000 len-400000.rom" > /tmp/revD_.txt

xxd "ROM Beige G3 rev D2/ROMs/@FFC00000 len-400000.rom" > /tmp/revD2_.txt

xxd -b -c 1 "ROM Beige G3 rev D/ROMs/@FFC00000 len-400000.rom" | sed -E 's/ .$//' > /tmp/revD.txt

xxd -b -c 1 "ROM Beige G3 rev D2/ROMs/@FFC00000 len-400000.rom" | sed -E 's/ .$//' > /tmp/revD2.txt

diff -y --suppress-common-lines /tmp/revD.txt /tmp/revD2.txt > /tmp/diff.txt

perl -pE 's/\w{7}(.).*/$1/' /tmp/diff.txt | sort | uniq -c

1 4

434 5

2 c

1580 d

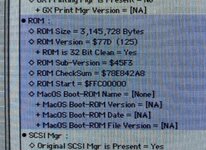

0038f21c: 10111011 | 0038f21c: 01001011

003fe07c: 00111000 | 003fe07c: 01001011

003fe084: 01001011 | 003fe084: 00111000

4 = 0100

C = 1100

5 = 0101

D = 1101

fputc(hhdata[offset + 1], outfile); fputc(hhdata[offset + 0], outfile); 000 001

fputc(hldata[offset + 1], outfile); fputc(hldata[offset + 0], outfile); 010 011

fputc(lhdata[offset + 1], outfile); fputc(lhdata[offset + 0], outfile); 100 101 <-- problems

fputc(lldata[offset + 1], outfile); fputc(lldata[offset + 0], outfile); 110 111