@mdeverhart Is it really necessary to _slow_ the signals? From the Atmel's datasheet for the G16V8, there's already a bit of variability there.

I _think_ (but with not a lot of confidence) that the one thing that matters is for the logic to be 'fast enough' to reach its destination in time. Being faster than the original should not be a problem.

I attach some automated conversion of @Bolle 's GAL code from the first post; 'u*.v' are the trivial translations, 'u*_opt.v' has been filtered to do some DeMorgan, double negation elimination, and 2-ary->n-ary conversion to be more readable. Very untested, there could be bugs in my quick'n'dirty translator.

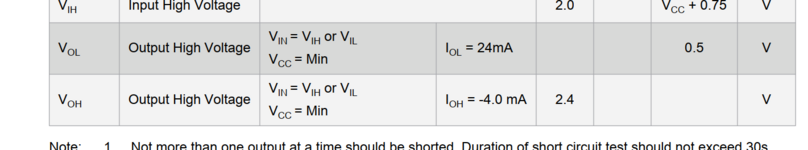

XC9536XL in speed grade -10 will match the fastest of the two G16V8 speed grade, and will be at least as fast or faster on almost every parameters (/OE to output enable/disable being the exception, you need to go one speed grade better as the CPLD is 11ns vs. the GAL 10ns).

Symbol Parameter Min (-10) Max(-10) Min (-15) Max (-15) Units tPD Input or Feedback to

Non-Registered Output

8 outputs switching3 10 3 15 ns

I _think_ (but with not a lot of confidence) that the one thing that matters is for the logic to be 'fast enough' to reach its destination in time. Being faster than the original should not be a problem.

I attach some automated conversion of @Bolle 's GAL code from the first post; 'u*.v' are the trivial translations, 'u*_opt.v' has been filtered to do some DeMorgan, double negation elimination, and 2-ary->n-ary conversion to be more readable. Very untested, there could be bugs in my quick'n'dirty translator.