(relevant information from Apple Developer Technical Support April 1992 Document)

4 Mbit DRAMs in Revolt

When the Macintosh II was originally designed, Apple engineers intended for it to accept large

amounts of memory in the form of 4 MB and 16 MB DRAM SIMMs. That was in 1986, when 1

Mbit DRAM was difficult to find and the higher-density chips did not yet exist. The engineers

anticipated the pinouts of the yet to be introduced 4 MB SIMMs and provided all the necessary

hardware and address multiplexing to allow installation of these parts when they became available.

Woe that Cupertino is not Camelot, James Brown is still on probation, and 4 MB SIMMs do not

work as advertised in most cases. This is the story of the Revolt of the 4 MB DRAM SIMMs.

Preliminary Notes

Before diving into the problem with 4 Mbit DRAMs, there is some preliminary ground that must be

covered.

First, there are a couple ways to construct a 4 MB SIMM. Using old technology, it is possible to

cram together 32 DRAM ICs of 1M x 1 density. Using new technology, it only takes eight 4M x 1

ICs, resulting in a much smaller, lower-power module. If a 4 MB SIMM is of the large, so-called

composite type (that is, it is constructed of 32 1 Mbit ICs), then everything is fine except on the

original Macintosh II. Please refer to page 7 of this Tech Note for more information on Macintosh

II RAM.

With the FDHD SuperDrive upgrade kit installed, the Macintosh II is on equal footing with the

Macintosh IIx. That is, SIMMs made exclusively of the new 4 Mbit ICs still won’t work,

regardless of whether you are using a Macintosh II or IIx; therefore, for the remainder of this

discussion, Macintosh II is used to refer to not only the original Macintosh II, but also the IIx.

Subsequent Macintosh models have revised ROMs that recognize 4 MB SIMMs.

The 4 Mbit Problem

DRAM ICs are now available in 4 Mbit density, but they come with a very nasty surprise. JEDEC,

the committee overseeing the standardization of new solid-state devices, has added an additional

built-in test mode to high-density DRAMs. The test mode is invoked by a sequence of electrical

signals that was ignored by earlier-generation DRAM. The crux of the situation is this: under

certain conditions, the Macintosh II unwittingly activates this new test mode and large amounts of

memory become very forgetful.

More Specifically . . .

Those who are interested in the specific phenomenon occurring within the memory ICs should

consult the detailed technical data supplied by the DRAM manufacturers. This Note only explains

how the Macintosh II offends this new feature of the 4 Mbit DRAM, and hence, what might be

done to work around the problem.

The Macintosh II uses /CAS-before-/RAS refresh cycles to keep RAM up to date on its contents.

For 1 Mbit DRAM, the state of the /W control line is ignored during this type of refresh cycle. No

longer. DRAM of the 4 Mbit variety goes off into test mode if /W is asserted (low, so that the

RAM thinks it is write-enabled) during a /CAS-before-/RAS refresh cycle. The problem with the

Macintosh II is that /W is the same signal as the MPU R/W line, and if the MPU is writing to an

I/O address or a NuBus™ card concurrently with a refresh cycle, all the conditions are right for a

waltz into test mode. Unfortunately, this condition is not all that unusual, since video card accesses

qualify

Consolation for SIMM manufacturers: SIMMs constructed with an on-board PAL are not

necessarily Macintosh II-specific. SIMMs constructed in this manner should work without

modification in any usage calling for 4 MB SIMMs (except in the unlikely event that the new test

mode is required).

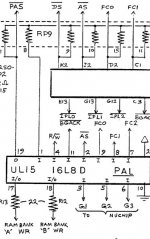

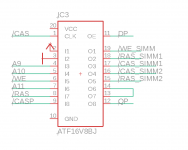

The Salvage Process

All is not necessarily lost, and although the situation is ugly, there is still a way to use 4 Mbit

DRAM ICs to construct 4 MB SIMMs that work in the Macintosh II. A solution lies in the addition

of a ninth IC to the SIMM. Programmed with suitable logic, a high-speed (-D or -E suffix) PAL on

the SIMM itself can recognize and intercept /CAS-before-/RAS refresh cycles and set /W

appropriately before any damage is done. More or less, the PAL becomes an intelligent buffer

between the MPU read/write line and the DRAM write-enable lines. When the PAL senses a

refresh cycle commencing, it holds /W high, ensuring that the ICs are not corrupted by the

potentially dangerous processor-generated R/W signal.

What’s the Point?

You have overcome all the problems discussed in this section and have working 4 Mbit SIMMs

installed in your Macintosh. You probably have at least 20 MB of RAM. What can you do with all

of it? Create lots of huge 32-bit PICTs and edit them all simultaneously? Model and animate Bay

Area weather patterns in Mathematica™? Yes! But, you have to use the appropriate system software

to address this memory. Also, if you’re running in 32-bit addressing mode, the applications that

you desire to use need to be 32-bit clean. For more information on 32-bit cleanliness and

addressing, please see Technical Notes #212 and #213.

Under System 7.0, applications can finally access additional physical memory over and above 8

MB. As mentioned previously in this Tech Note, the 32-bit addressing mode of System 7 requires

either a Macintosh with 32-bit clean ROMs (listing is on page 2), or else the 32-bit software

solution provided by the MODE32 system extension. A/UX is an alternative that can use up to

256K of RAM on Macintosh computers that support A/UX. Many manufacturers of large SIMMs

also offer RAM disks. This is a volatile form of storage, but can certainly be useful for I/O

intensive operations.

Other Permutations

The problem with 4 Mbit DRAM is not limited to 4 MB SIMMs. It is the 4 Mbit density of the

individual RAM ICs that causes problems with certain machines. There exist 1 MB SIMMs

constructed of only two 1M x 4 (4 Mbit) ICs. These do not work in a Macintosh II or IIx, any

more than 4 MB SIMMs constructed of eight 4M x 1 ICs.

A few machines, namely the Macintosh Plus, Macintosh SE, and Macintosh Classic, depend on

video accesses to refresh all of their DRAM. As the video circuitry accesses sequential locations

through the video frame buffer, it simultaneously refreshes row after row of memory, eventually

refreshing all 512 rows. Memory at the 4 Mbit density, however, is arranged as 1024 rows and

there are not sufficient video accesses to refresh all 1024 rows. Chunks of memory simply go

blank. Thus for a different reason, 4 Mbit DRAM parts are also not compatible with these older

Macintosh hardware designs.

Executive Summary

Owners of the Macintosh Plus, SE, Classic, II, or IIx are all likely to have problems with any 1MB SIMM carrying only two ICs, or any 4 MB SIMM carrying only 8 ICs. Any SIMM constructed in one of these ways likely uses 4 Mbit density DRAM ICs and does not account for

problems with the 4 Mbit test mode nor the video refresh strategy of older Macintosh designs.