Trash80toHP_Mini

NIGHT STALKER

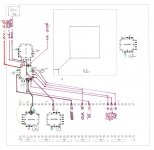

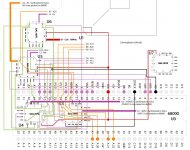

Rev 2 with corrected names and the bus moved out of the way. Eagle has a 68881, but not a 68882, so I may have to make one. Ugh.

View attachment 21506

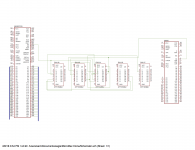

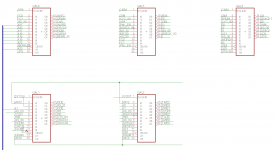

View attachment 21505

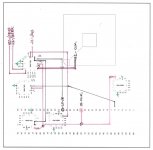

I like it! I can work with your conventional presentation as a DELTA Schematic, marking it up if the revisions don't match what I'm "seeing" in the PCB Trace modeling that works for the way my noggin' doesn't work quite right. Those who actually do electronics and digital development will be very glad to be able to read my crazy AI diagram Hieroglyphs in an actual, real world schematic diagram for a change. Thank you! [

As for the 68882, we don't need at all until we begin to close in on a near production level PCB design. Its pins should map 1:1 with the 68030, no? We don't want it cluttering up the DELTA Schematic. I'm only using it as a U2 placeholder in the component list for inclusion much later on in the process.

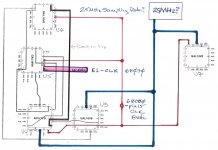

Mapping differentiation in control lines where they are engulfed by the GALS, their exit points after they are tweaked or are synthesized (like A0)) within the GAL Maelstrom. Some merely skirt the whirlpool as they are monitored by the GALS (like A19, A20 and A21 I've yet to document in AI) and more exceptional cases I may find like /AS.

/AS in its native 68000 state is monitored by U5 and is engulfed by U4 where there is a Logical disconnect. Within U4 it appears to be translated to a 68030 /AS state which is monitored by U6 on its way to the 68030.

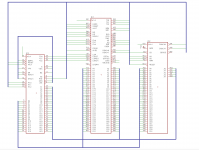

These two examples are what the DELTA Schematic is all about. If you pull those bus lines off the 68030 it would be a big help to me. [