Hello all,

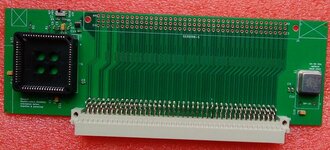

I've built for my IIsi a new PDS adapter with a 68882 FPU socket, PLCC version. I got myself a PLCC 68882 rated for 33 MHz from what I believe to be a reputable vendor on eBay.

My design includes an external 32 MHz oscillator (MXO45HS-3C-32M0000, couldn't find 33 MHz one in stock), and a small manual switch that drives a 74LVC1G3157 silicon switch so that the FPU clock comes from either the system clock or the on-board oscillator. I subsequently discovered that @Siliconinsider has a similar design for the Classic II, minus the silicon switch - as far as I can tell the clock goes through the jumper. Easier & cheaper & known to work, wish I had done the same, but oh well...

When I try it in my IIsi:

I should solder myself a second adapter with a 25 MHz oscillator (slowest I have in stock), but soldering another set of 192 pins is not something I look forward to (120 for the motherboard-side connector, 68 for the socket, 4 for the oscillator... I didn't solder the second 120-pins connector yet as I don't have a PDS card to test it with anyway).

(120 for the motherboard-side connector, 68 for the socket, 4 for the oscillator... I didn't solder the second 120-pins connector yet as I don't have a PDS card to test it with anyway).

I've built for my IIsi a new PDS adapter with a 68882 FPU socket, PLCC version. I got myself a PLCC 68882 rated for 33 MHz from what I believe to be a reputable vendor on eBay.

My design includes an external 32 MHz oscillator (MXO45HS-3C-32M0000, couldn't find 33 MHz one in stock), and a small manual switch that drives a 74LVC1G3157 silicon switch so that the FPU clock comes from either the system clock or the on-board oscillator. I subsequently discovered that @Siliconinsider has a similar design for the Classic II, minus the silicon switch - as far as I can tell the clock goes through the jumper. Easier & cheaper & known to work, wish I had done the same, but oh well...

When I try it in my IIsi:

- Set to system clock, TattleTech sees the FPU and Speedometer 4.02 produces FPU results as expected (slightly better than a SE/30).

- Set to my own oscillator, TattleTech sees the FPU, and Speedometer insta-crash with error 11.

I should solder myself a second adapter with a 25 MHz oscillator (slowest I have in stock), but soldering another set of 192 pins is not something I look forward to