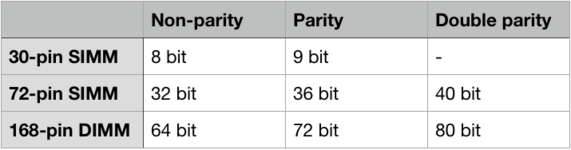

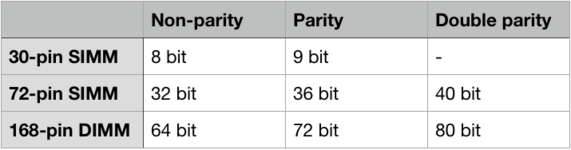

Here's a quick note with the module bus width. Provision for double parity exist in the JEDEC standard and is mostly used by IBM, they are rare but they do exist. Any modules that will have a different number than 2, 4, 8 16, 32 memory chips on them will have a good chance to have parity.

Other variations:

- Fast Page Mode (FPM) or Extended Data Out (EDO), modes to read entire consecutive memory pages without refreshing the address for faster access. EDO is capable of FPM so EDO RAM will work in FPM only systems, but system that specifically make use of EDO will need EDO.

- Voltage, 5V or 3.3V, these are not interchangeable, and the module is keyed to prevent insertion.

- Buffered/registered, the address bus goes through a buffer which is usually seen as 1-2 smaller chips in the middle of DIMMs. These help to share the load as in systems with a lot of memory slots and DRAM chips on the modules, all the address lines for each chips are in parallel. This is transparent to the system but it is preferable.

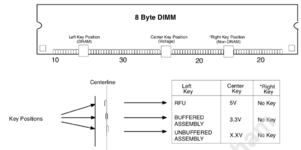

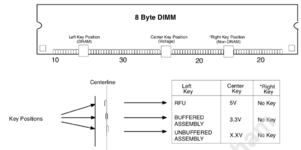

Last, DIMM modules are keyed. The position of the notch will be centred, or offset to the left or right. you can identify them using this way.

The left key is for the buffered/unbuffered identification, the middle key is for the operating voltage. The right key does not exist on DRAM modules.