I did not expect success with my first try.

First image is with stock Mac 512k 64mb ROM - No chime and steady screen distortion.

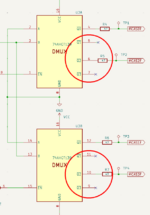

Second image is with ST M27C512 ROM's with Mac 512k flash. - No chime. Distorted Growl, then screen would flash, then go blank. This would repeat.

Any suggestions would be appreciated. The ROM-inator PCB's arrive this afternoon. I will put together one and check again later this afternoon.

First image is with stock Mac 512k 64mb ROM - No chime and steady screen distortion.

Second image is with ST M27C512 ROM's with Mac 512k flash. - No chime. Distorted Growl, then screen would flash, then go blank. This would repeat.

Any suggestions would be appreciated. The ROM-inator PCB's arrive this afternoon. I will put together one and check again later this afternoon.